Threshold Multi Split-Row algorithm for decoding irregular LDPC codes

Volume 2, Issue 5, Page No 88–93, 2017

Adv. Sci. Technol. Eng. Syst. J. 2(5), 88–93 (2017);

DOI: 10.25046/aj020514

DOI: 10.25046/aj020514

Keywords: LDPC codes, Threshold Multi Split-Row, algorithm, Multi Split-Row algorithm

In this work, we propose a new threshold multi split-row algorithm in order to improve the multi split-row algorithm for LDPC irregular codes decoding. We give a complete description of our algorithm as well as its advantages for the LDPC codes. The simulation results over an additive white gaussian channel show that an improvement in code error performance between 0.4 dB and 0.6 dB compared to the multi split-row algorithm.

1 Introduction

Low-density parity check (LDPC) codes are a class of linear block codes, which were first, introduced by gallager in 1963 [1]. As soon as they were re-invented in 1996 by mackay [2], LDPC codes have received a lot of attention because their error performance is very close to the shannon limit when decoded using iterative methods [3]. They have emerged as a viable option for forward error correction (FEC) systems and have been adopted by many advanced standards, such as 10 gigabit ethernet (10GBASET) [4], [5] and digital video broadcasting (DVB-S2) [6], [7]. In addition, the generations of WiFi and WiMAX are considering LDPC codes as part of their error correction systems [8], [9].

In the present paper, we propose the threshold multi split-row method for decoding irregular lowdensity parity-check (LDPC) codes [10], to have better performance in terms of bit error rate. We will apply the thresholding algorithm in [11] for multi split row of irregular LDPC codes[10]. The proposed split-row decoder [10],[11] splits the row processing into two or multiple nearly independent partitions. Each block is simultaneously processed using minimal information from an adjacent partition. The key idea of split-row is to reduce communication between row and column processors which has a major role in the interconnect complexity of existing LDPC decoding algorithms such as sum product (SPA) [3] and minsum (MS) [12]. This paper introduces threshold multi split-row decoding which significantly reduces wire interconnect complexity and considerably improves the error performance compared to non-threshold multisplit decoding [10]. The paper is organized as follows: Section II reviews the sum product and minsum, split-row and split-row threshold decoding algorithms. Threshold multi-split-row and its error performance result is presented in section III. Finally, the conclusion is in section IV.

2 Previous algorithms

2.1 Sum Product Decoding(SPD)

The SPD assumes a binary code word (x1;x2; :::;xN) transmitted using a binary phase-shift keying (BPSK) modulation. The sequence is transmitted over an additive white gaussian noise (AWGN) channel and the received symbol is (y1;y2; :::;yN). We define:

V(i) = fj : Hij = 1g as the set of variable nodes which participate in the check equation i. C(j) = fi : Hij = 1g as the set of check nodes which participate in the variable node j update.

Also

V(i) n j denote all variable nodes in V(i) except node j.

C(j) \ i denote all check nodes in C(j) except node i. Moreover, we define the following variables used in this paper.

λj : is defined as the information derived from the

log-likelihood ratio of received symbol yj.

λj = log(P (xi = 0|yj)/P (xi = 1|yj)) = (2yj)/σ2 (1)

where σ2 is the noise variance. αij is the message from check node i to variable node j. This is the row processing output. βij is the message from variable node j to check node i. This is the column processing output.

The sum product algorithm decoding as described by mohsenin and Baas [13], can be summarized in the following four steps:

2.1.1 Initialization

For each i and j, initialize βij to the value of the loglikelihood ratio of the received symbol yj, which is λj. During each iteration, αβ messages are computed and exchanged between variables and check nodes through the graph edges according to the following steps numbered 2-4.

- Row processing or check node updateCompute αij messages using β messages coming from all other variable nodes connected to check node Ci,

| excluding the β information from Vj: | |

| Y

αij = sign(βij0 ) × φ(Σj0 ∈V (i)\jφ(|βij0 |)) 0 j ∈V (i)\j where the non-linear function |

(2) |

| φ(x) = −log(tanh(|x|/2)) | (3) |

The first product term in the equation that update the parameter, is called the parity (sign) update and the second product term is the reliability (magnitude) update.

- Column processing or variable node updateCompute βij messages using channel information λj and incoming, messages α; from all other check nodes connected to variable node Vj, excluding check node

Ci.

βij = λj +Σi0 ∈C(j)\iα(i0 j) (4)

- Syndrome check and early terminationWhen the column processing is finished, every bit in column j is updated by adding the channel information λj and α, messages from neighboring check nodes.

zj = λj +Σi0 ∈C(j)α(i0 j) (5)

From the updated vector, an estimated code vector

Xb= {bx1,bx2,…,bxN } is calculated by:

i

If H ×bxt = 0 then Xb is a valid codeword and therefore the iterative process has converged and decoding stops. Otherwise, the decoding repeats from step 2 until a valid codeword is obtained or the number of iterations reaches a maximum number, which terminates the decoding process.

2.2 MinSum Decoding

The check node or row processing stage of SP decoding can be simplified by approximating the magnitude computation in Eq. 2 with a minimum function. The algorithm using this approximation is called minsum (MS):

Y

αij = sign(βij0 ) × Minj0 ∈V (i)\j(|βij0 |) (7)

0

j ∈V (i)\j

In MS decoding, the column operation is the same as in SP decoding. The error performance loss of MS decoding can be improved by scaling the check (α) values in Eq. 7 with a scale factor S ≤ 1 which normalizes the approximations [14], [15].

Y

αij = S × sign(βij0 ) × Minj0 ∈V (i)\j(|βij0 |) (8)

0

j ∈V (i)\j

2.3 Split Row and Split Row Threshold Decoding

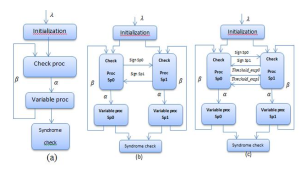

Recall that a standard message passing two-phase algorithm consists of a check node update followed by a variable node update as shown in Fig. 1 (a). The basic idea in split-row [10], [16] and split-row threshold [11], is to divide the check node processing into two or multiple nearly-independent partitions. Each check node processor, simultaneously, computes a new message while using minimal information from its adjacent partitions. Split-row is illustrated in Fig. 1 (b) showing how the check node processing is partitioned into two blocks. A single bit of information (Sign) for each check node processor must be sent between partitions to improve the error performance.

Figure 1. Block diagram of (a) standard two-phase decoding (b) split-row (c) split-row threshold block diagram.

Figure 1. Block diagram of (a) standard two-phase decoding (b) split-row (c) split-row threshold block diagram.

The loss error performance is 0.5-0.7 dB of split-row that is the major drawback, when compared to minsum normalized and SPA decoders. This performance degradation is dependent on the number of check node partitions. For minsum split-row each partition has no information of the minimum value of the other partition, and a Sign signal is sent to minimize the error due to incorrect sign information of the true check node output α.

The split-row threshold algorithm mitigates the error caused by incorrect magnitude by providing a signal, threshold en, which indicates whether a partition has a minimum less than a given threshold (T).This causes all check nodes to take the min of their own local minimum or T. Thus, any large deviations from the true minimum because of the partitioning are reduced, which then makes multi-split implementations feasible.

Figure 1 (c) shows the additional single bit signal (threshold en ) added to the original split-row architecture by the split-row threshold algorithm. This signal allows the split-row to remain essentially unchanged while adding some extra logic and minimal wiring to improve error significantly [11].

Therefore, the split-row architectures reduce the communication between check node and variable node processors, which is the major cause of the interconnect complexity found in existing LDPC decoder implementations.In addition, the area of each check node processor will be reduced. However, note that the variable node operation in the SPA, minsum, splitrow and split-row threshold algorithms are all identical. Thus, the logic of the variable node processor is left unchanged.

3 Threshold Mutli Split Row Decoding

3.1 Threshold Mutli Split Row Algorithm

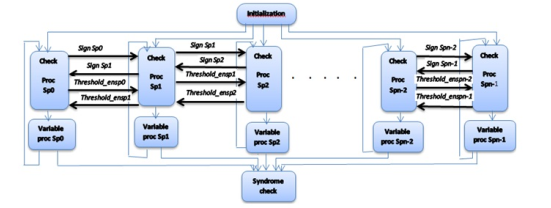

In order to increase the parallelism and reduce the complexity of the decoder, the multi-split-row method divides the lines of the systematic submatrix Hs into Spn blocks called split-Spn. This approximation requires of the wire to correctly process the sign bits between the blocks. For the threshold multi split-row method, Each partition sends the status of its local minimum against a threshold to the next partition with a single wire, called T hreshold ensp.

The block diagram of threshold multi split-row decoding with Spn partitions, highlighting the sign and T hreshold ensp passing signals, is shown in Fig. 2. These are the only wires passing between the partitions [17]. In each partition, local minimums are generated and compared with a threshold T simultaneously. If the local minimum is smaller than T then the T hreshold ensp signal is asserted high. The magnitudes of the check node outputs are finally computed using local minimums and the T hreshold ensp signal from neighboring partitions.

0

If a local partition s minimums are larger than T , and at least one of the T hreshold ensp signals is high, then T is used to update its check node outputs. Otherwise, local minimums are used to update check node outputs.

in the threshold multi split-row algorithm, as shown in Eq. (10) and (11), the first and second Mins are compared with a predefined threshold, and a single-bit threshold-enable (T hreshold en out) global signal is sent to indicate the presence of a potential global minimum to other partitions.

3.1.1 Initialization

The first and second minimums are determined for each partition according to the following relationships:

Minj0 ∈V (i)\j(|βij0 |) = ( MinMin12ii;; ifif ;; jj ,= argminargmin((MinMin11ii))

Figure 2. Block diagram of threshold multi split row decoding with Spn partitions. Figure 2. Block diagram of threshold multi split row decoding with Spn partitions. |

(9)

Min1i = minj∈V (i)(|βij0 |) (10)

Min2i = minj00 ∈V (i)\argmin(min1i)(|βij00 |) (11) to execute the algorithm one needs the number of partitions and the threshold value T. Finds T hreshold ensp(i) out(i∓1) for the ith partition of a spn-decoder.

Algorithm 1 Threshold Multi Split-Row Algorithm

1-if Min1i ≤ T and Min2i ≤ T then

Threshold ensp(i) out(i ∓ 1) = 1

Minj0 ∈V(i)\j(|βij0 |) = ( MinMin21ii if jif j ,=argminargmin((MinMin11ii)) (12)

- if Min1i ≤ T and Min2i ≥ T then

Threshold ensp(i) out(i ∓ 1) = 1 Threshold ensp(i +1) == 1 or

Threshold ensp(i − 1) == 1 then

Minj0 ∈V(i)\j(|βij0 |) = ( MinT if1i jif= argminj , argmin(Min(Min1i) 1i) (13)

| else | |

| (

Min1 Minj0 ∈V(i)\j(|βij0 |) = Min2ii ifif end if |

j , argmin(Min1i) j = argmin(Min1i) |

- else if Min1i ≥ T and (Threshold ensp(i +1) == 1 or

Threshold ensp(i − 1) == 1) then Threshold ensp(i) out(i ∓ 1) = 0

Minj0 ∈V(i)\j(|βij0 |) = T (14)

- else

Threshold ensp(i) ou(i ∓ 1) = 0

i if j , argmin(Min1i) (15) i if j = argmin(Min1i)

end if.

The kernel of the threshold multi split-row algorithm is given in Algorithm 1. As shown, four conditions will occur:

Condition 1: both Min1 and Min2 are less than threshold T. In this case these 2 parameters are used to calculate α messages according to Eq.(12). In addition, T hreshold ensp(i) out(i∓1), which represents the general threshold-enable signal of a partition with two neighbors, is asserted high indicating that the least minimum (Min1) in this partition is smaller than T.

Condition 2: only Min1 is less than T. As Condition 1 T hreshold ensp(i) out(i∓1)= 1. If at least one T hreshold ensp(i ∓ 1) signal from the nearest neighboring partitions is high, indicating that the local minimum in the other partition is less than T, then we use Min1 and T to calculate α messages according to Eq.(13). Otherwise, we use Eq.(12).

Condition 3: when the local Min1 is larger than T and at least one T hreshold ensp(i∓1) signal from the nearest neighboring partitions is high; thus, we only use T to compute all α messages for the partition using

Eq.(14).

Condition 4: when the local Min1 is larger than T and if the T hreshold ensp(i∓1) signals are all low; thus, we again use Eq.(12).

The variable node operation in minsum threshold multi split-row algorithm is identical to the minsum normalized and minsum multi split-row algorithms.

3.2 BER Simulation Results

The error performance simulations presented here assume an additive white gaussian noise (AWGN) channel with binary phase-shift keying (BPSK) modulation. The maximum number of iterations is set to Imax = 7 or earlier when the decoder converged [11]. We fix the threshold Imax to satisfy a tradeoff between the performance correction and the speed of the decoder.

The following labelings are used for the figures:

“MS Standard” for normalized minsum, “MS Multi Split-Row” for the method minsum multi split-row algorithm, and “S” for the scaling factor. The performances of irregular LDPC codes are illustrated in the figure given below.

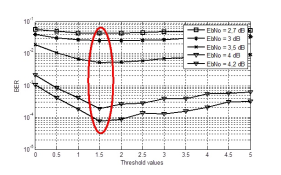

The error performance depends strongly on the choice of threshold T values and the scaling factor S. The optimum values for T and S are obtained by empirical simulations as illustrated in the following figures.

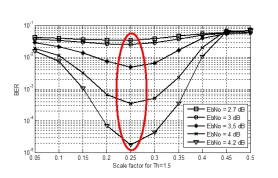

The figure 3 shows the simulation to determine experimentally the threshold for minsum threshold multi split-row of the LDPC code (6,18) (1536,1152). with:

Code length N= 1536.

Information length K=1152.

Column weight Wc = 6 which is the number of ones per column.

Row weight Wr =18 which is the number of ones per row.

The threshold optimum value for an SNR ranging from 2.7 dB to 4.2 dB, with the value of the normalization factor S = 0.25 obtained in figure 6, is 1.5.

Figure 3. BER (Bit error rate) performance in function of the threshold for different SNR (Signal to noise ratio) values.

Figure 3. BER (Bit error rate) performance in function of the threshold for different SNR (Signal to noise ratio) values.

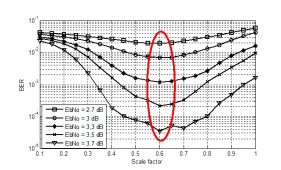

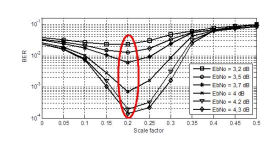

Figures 4 and 5 show the simulation to determine experimentally the scaling factor for normalized minsum and minsum multi split-row, respectively, of the LDPC code (6,18) (1536,1152) . Optimal scale factor, for normalized minsum, is 0.6. And optimal scale factor, for minsum multi split-row, is 0.2.

Figure 4. BER (Bit error rate) performance in function of the scale factor using normalized minsum for different SNR (Signal to Noise Ratio) values.

Figure 4. BER (Bit error rate) performance in function of the scale factor using normalized minsum for different SNR (Signal to Noise Ratio) values.

Figure 5. BER (Bit error rate) performance in function of the Scale factor using minsum multi split-row for different SNR (Signal to noise ratio) values.

Figure 5. BER (Bit error rate) performance in function of the Scale factor using minsum multi split-row for different SNR (Signal to noise ratio) values.

Figure 6 shows the simulation to determine experimentally the scaling factor for minsum threshold multi split-row of the LDPC code (6,18)(1536,1152). Optimal scale factor is 0.25 with the threshold T=1.5.

Figure 6. BER (Bit error rate) performance in function of the scale factor using minsum threshold multi split-row for different SNR (Signal to noise ratio) values.

Figure 6. BER (Bit error rate) performance in function of the scale factor using minsum threshold multi split-row for different SNR (Signal to noise ratio) values.

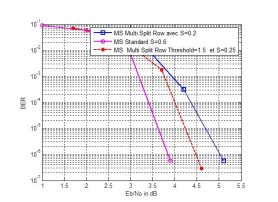

Figure 7 shows the error performance results for a (6,18) (1536,1152) LDPC code for different decoding algorithms (minsum normalized, minsum multi splitrow and minsum threshold multi split-row). The code rate is R=0.75 and the maximum number of iteration is set to Imax = 7, with threshold values obtained in Fig.3 and scale factors obtained in Fig.4, Fig.5 and

Fig.6.

Figure 7. BER performance of (6,18) (1536,1152) irregular code using various decoding algorithms.

Figure 7. BER performance of (6,18) (1536,1152) irregular code using various decoding algorithms.

As shown in the figure, minsum threshold multi splitrow with optimal threshold T = 1.5 performs about 0.6 dB better than minsum multi split-row and is only 0.7 dB away from MinSum normalized at BER =

6.10−7.

The minsum threshold multi split-row algorithm utilizes a threshold-enable signal to compensate for the loss of min() interpretation information in multisplit-row algorithm. It provides at least 0.6 dB error performance over the multi-split-row algorithm with Spn = 4. Partitioning the parity matrix in Spn blocs allows us to increase the decoder’s parallelism. Therefore, the partitions are performed simultaneously and we obtained a parallel decoder. That means,the complexity decreases and the decoding becomes faster.

As shown in Figure 7, the better performance gap indicated between the minsum threshold multi splitrow and minsum multi split-row algorithm revert to the information passed from one partition to another (Threshold ensp) in algorithm threshold multi splitrow, which reduces difference between the local minimum in each partition and the first and second global minimums.

4 Conclusion

In this paper we have extended threshold multi splitrow decoding method used for regular LDPC code to the irregular LDPC code. The aims was to improve the errors performances of the decoder. Simulation results show that the threshold multi split-row outperforms the multi split-row algorithm for 0.6 dB while maintaining the same level of complexity (only the comparison between the threshold and the first and second minimums is added). Our simulation results show that for a given LDPC code keeping threshold T constant at any SNR does not cause any error performance degradation.

- G. Gallager, “Low-Density-Parity-Check,”,IRE Trans. Information Theory, vol. II, no. 8, pp. 21-28, Jan 1962.

- MacKay et R. M. Neal, “Near Shanon Limit Performance of Low-Density-Parity-Check Codes,” ,Electron. Lett., vol. 32, pp. 1645-1946, Aug. 1996

- J. C. MacKay, “Good error-correcting codes based on very sparse matrices,”,IEEE Trans. Inform. Theory, vol. 45, p. 399-432, Mar. 1999.

- “IEEE 802.3an, standard for information technologytelecommunications and information exchange between systems”.

- Cohen, A.E., Parhi and K.K,“A Low-Complexity Hybrid LDPC Code Encoder for IEEE 802.3an (10GBase- T) Ethernet,”,IEEE Transactions on Signal Processing, vol. 57, no. 10, pp. 4085-4094, 2009.

- “T.T.S.I. digital video broadcasting (DVB) second generation framing structure for broadband satellite applications,”[ Online].

- -M. Kim, C.-S. Park and S.-Y. Hwang,“A Novel Partially Parallel Architecture for High-Throughput LDPC Decoder for DVB-S2,”,IEEE Transactions on Con-sumer Electronics, vol. 56, no. 2, pp. 820-825, May 2010.

- -L. Wang, Y.-L. Ueng, C.-L. Peng and C.-J. Yang, “A Low-Complexity LDPC Decoder Architecture for WiMAX Applications,”,in Proc. of the Int. Symp on VLSI Design, Automation and Test, Hsinchu, April 2011.

- -W. Shin and H.-J. Kim,“A Multi-Mode LDPC Decoder for IEEE 802.16e Mobile WiMAX,”, Journal of Semiconductor Technology and Science, vol. 12, no. 1, pp. 24-33, Mar. 2012.

- ElAlami and M. Mrabti,“Reduced Complexity of Decoding Algorithm for Irregular LDPC Codes Using a Multiple Split Row Method,”, International Journal of Research and Reviews in Mechatronic Design and Simulation, vol. 1, no. 1, pp. 12-17, March 2011.

- ElAlami, H. Qjidaa, Y. Mehdaoui and M. Mrabti,“A Thresholding Algorithm for Improved Split-Row Decoding Method of Irregular LDPC Codes,”,in Proc. Of the The IEEE International Conference on Intelligent Systems and Computer Vision 2015, Fez, Morocco, March 2015.

- Fossorier, M. Mihaljevic and H. Imai,“Reduced Complexity Iterative Decoding of Low-Density Parity-Check Codes Based on Belief Propagation,”, IEEE Transactions on Communications, vol. 47, no. 5, pp. 673-680, May 1999.

- Mohsenin T, Baas B.“Split-row: a reduced complexity, high throughput LDPCdecoder architecture,”, Proceedings of the ICCD, October. 2006.

- Chen and M. Fossorier,“Near optimum universal belief propagation based decoding of low-density parity check codes,”, IEEE Transaction Communications, vol. 50, pp. 406-414, Mar. 2002.

- Chen, A. Dholakia, E. Eleftheriou, and M. Fossorier,“Reduced complexity decoding of LDPCcodes,”,IEEE Transaction Communications, vol. 53, pp. 1288-1299, Aug. 2005.

- ElAlami, M. Mrabti and C. B. Gueye,“Reduced Complexity of Decoding Algorithm for Irregular LDPC Codes Using a Split Row Method,”,Journal of Wireless Networking and Communications, vol. 4, no. 2, pp. 29-34, 2012.

- Mohsenin, D. Truong, and B. Baas, “Multi-splitrow threshold decoding implementations for LDPC codes,” in Proc. ISCAS, May 2009,pp. 2449-2452.

- Chiang Ling Feng, "Optimization of Sheet Material Layout in Industrial Production Using Genetic Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 10, no. 5, pp. 51–65, 2025. doi: 10.25046/aj100506

- Abdulrasaq Jimoh, Samson Oladayo Ayanlade, Emmanuel Idowu Ogunwole, Dolapo Eniola Owolabi, Abdulsamad Bolakale Jimoh, Fatina Mosunmola Aremu, "Metaheuristic Optimization Algorithm Performance Comparison for Optimal Allocation of Static Synchronous Compensator", Advances in Science, Technology and Engineering Systems Journal, vol. 8, no. 1, pp. 116–124, 2023. doi: 10.25046/aj080114

- Amine Bouaouda, Karim Afdel, Rachida Abounacer, "Meta-heuristic and Heuristic Algorithms for Forecasting Workload Placement and Energy Consumption in Cloud Data Centers", Advances in Science, Technology and Engineering Systems Journal, vol. 8, no. 1, pp. 01–11, 2023. doi: 10.25046/aj080101

- Tarek Nouioua, Ahmed Hafid Belbachir, "The Security of Information Systems and Image Processing Supported by the Quantum Computer: A review", Advances in Science, Technology and Engineering Systems Journal, vol. 7, no. 6, pp. 77–86, 2022. doi: 10.25046/aj070609

- Thilini Lakshika, Amitha Caldera, "Association Rules for Knowledge Discovery From E-News Articles: A Review of Apriori and FP-Growth Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 7, no. 5, pp. 178–192, 2022. doi: 10.25046/aj070519

- Marzouk Hassan, Abdelmajid Badri, Aicha Sahel, "A Self-Adaptive Routing Algorithm for Real-Time Video Transmission in VANETs", Advances in Science, Technology and Engineering Systems Journal, vol. 7, no. 5, pp. 91–101, 2022. doi: 10.25046/aj070512

- Basharat Jamil, Lucía Serrano-Luján, José Manuel Colmenar, "On the Prediction of One-Year Ahead Energy Demand in Turkey using Metaheuristic Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 7, no. 4, pp. 79–91, 2022. doi: 10.25046/aj070411

- Afsah Sharmin, Farhat Anwar, S M A Motakabber, Aisha Hassan Abdalla Hashim, "A Secure Trust Aware ACO-Based WSN Routing Protocol for IoT", Advances in Science, Technology and Engineering Systems Journal, vol. 7, no. 3, pp. 95–105, 2022. doi: 10.25046/aj070311

- Xiqin Lu, Nobuo Funabiki, Htoo Htoo Sandi Kyaw, Ei Ei Htet, Shune Lae Aung, Nem Khan Dim, "Value Trace Problems for Code Reading Study in C Programming", Advances in Science, Technology and Engineering Systems Journal, vol. 7, no. 1, pp. 14–26, 2022. doi: 10.25046/aj070103

- Wided Hechkel, Brahim Maaref, Néjib Hassen, "Coupled Apodization Functions Applied to Enhance Image Quality in Ultrasound Imaging using Phased Arrays", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 5, pp. 149–157, 2021. doi: 10.25046/aj060517

- Arwa Alghamdi, Graham Healy, Hoda Abdelhafez, "Machine Learning Algorithms for Real Time Blind Audio Source Separation with Natural Language Detection", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 5, pp. 125–140, 2021. doi: 10.25046/aj060515

- Olena Nosovets, Vitalii Babenko, Ilya Davydovych, Olena Petrunina, Olga Averianova, Le Dai Zyonh, "Personalized Clinical Treatment Selection Using Genetic Algorithm and Analytic Hierarchy Process", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 4, pp. 406–413, 2021. doi: 10.25046/aj060446

- Randy Kuang, Dafu Lou, Alex He, Alexandre Conlon, "Quantum Secure Lightweight Cryptography with Quantum Permutation Pad", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 4, pp. 401–405, 2021. doi: 10.25046/aj060445

- Jong-Jin Kim, Sang-Gil Lee, Cheol-Hoon Lee, "A Scheduling Algorithm with RTiK+ for MIL-STD-1553B Based on Windows for Real-Time Operation System", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 4, pp. 385–394, 2021. doi: 10.25046/aj060443

- Abdulkarim Saleh Masoud Ali, Rozmie Razif Othman, Yasmin Mohd Yacob, Haitham Saleh Ali Ben Abdelmula, "An Efficient Combinatorial Input Output-Based Using Adaptive Firefly Algorithm with Elitism Relations Testing", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 4, pp. 223–232, 2021. doi: 10.25046/aj060426

- Hathairat Ketmaneechairat, Maleerat Maliyaem, Chalermpong Intarat, "Kamphaeng Saen Beef Cattle Identification Approach using Muzzle Print Image", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 4, pp. 110–122, 2021. doi: 10.25046/aj060413

- Kohki Nakane, Rentaro Ono, Hiroki Takada, "Numerical Analysis for Feature Extraction and Evaluation of 3D Sickness", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 2, pp. 949–955, 2021. doi: 10.25046/aj0602108

- Van-Truong Nguyen, Anh-Tu Nguyen, Viet-Thang Nguyen, Huy-Anh Bui, Xuan-Thuan Nguyen, "Real-time Target Human Tracking using Camshift and LucasKanade Optical Flow Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 2, pp. 907–914, 2021. doi: 10.25046/aj0602103

- Ahmad AA Alkhatib, Abeer Alsabbagh, Randa Maraqa, Shadi Alzubi, "Load Balancing Techniques in Cloud Computing: Extensive Review", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 2, pp. 860–870, 2021. doi: 10.25046/aj060299

- : Mourad Fariss, Naoufal El Allali, Hakima Asaidi, Mohamed Bellouki, "An Improved Approach for QoS Based Web Services Selection Using Clustering", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 2, pp. 616–621, 2021. doi: 10.25046/aj060270

- Khalil Ibrahim Mohammad Abuzanouneh, Khalil Hamdi Ateyeh Al-Shqeerat, "Development and Improvement of Web Services Selections using Immigrants Scheme of Multi-Objective Genetic Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 2, pp. 412–422, 2021. doi: 10.25046/aj060248

- Amany Khalil, Osama Tolba, Sherif Ezzeldin, "Design Optimization of Open Office Building Form for Thermal Energy Performance using Genetic Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 2, pp. 254–261, 2021. doi: 10.25046/aj060228

- Abdelaziz Lberni, Malika Alami Marktani, Abdelaziz Ahaitouf, Ali Ahaitouf, "Multi-Objective Design of Current Conveyor using Optimization Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 2, pp. 154–160, 2021. doi: 10.25046/aj060218

- Subash Pokharel, Aleksandar Dimitrovski, "Ferromagnetic Core Reactor Modeling and Design Optimization", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 1, pp. 810–818, 2021. doi: 10.25046/aj060190

- Jesus Aguila-Leon, Cristian Chiñas-Palacios, Carlos Vargas-Salgado, Elias Hurtado-Perez, Edith Xio Mara Garcia, "Particle Swarm Optimization, Genetic Algorithm and Grey Wolf Optimizer Algorithms Performance Comparative for a DC-DC Boost Converter PID Controller", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 1, pp. 619–625, 2021. doi: 10.25046/aj060167

- Theerayod Wiangtong, Sethakarn Prongnuch, Suchada Sitjongsataporn, "Stochastic Behaviour Analysis of Adaptive Averaging Step-size Sign Normalised Hammerstein Spline Adaptive Filtering", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 1, pp. 577–586, 2021. doi: 10.25046/aj060162

- Abdelouahad Bellat, Khalifa Mansouri, Abdelhadi Raihani, Khalili Tajeddine, "Optimizing the Wind Farm Layout for Minimizing the Wake Losses", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 1, pp. 309–315, 2021. doi: 10.25046/aj060135

- Abdurazaq Elbaz, Muhammet Tahir Güneşer, "Optimal Sizing of a Renewable Energy Hybrid System in Libya Using Integrated Crow and Particle Swarm Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 1, pp. 264–268, 2021. doi: 10.25046/aj060130

- Minkyung Kim, Kangseok Kim, Jai-Hoon Kim, "Analysis of Real-time Blockchain Considering Service Level Agreement (SLA)", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 1, pp. 218–223, 2021. doi: 10.25046/aj060124

- Lonia Masangu, Ashwini Jadhav, Ritesh Ajoodha, "Predicting Student Academic Performance Using Data Mining Techniques", Advances in Science, Technology and Engineering Systems Journal, vol. 6, no. 1, pp. 153–163, 2021. doi: 10.25046/aj060117

- Olorunshola Oluwaseyi Ezekiel, Oluyomi Ayanfeoluwa Oluwasola, Irhebhude Martins, "An Evaluation of some Machine Learning Algorithms for the detection of Android Applications Malware", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1741–1749, 2020. doi: 10.25046/aj0506208

- Afsah Sharmin, Farhat Anwar, S M A Motakabber, "Efficient and Scalable Ant Colony Optimization based WSN Routing Protocol for IoT", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1710–1718, 2020. doi: 10.25046/aj0506204

- Karamath Ateeq, Manas Ranjan Pradhan, Beenu Mago, "Elasticity Based Med-Cloud Recommendation System for Diabetic Prediction in Cloud Computing Environment", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1618–1633, 2020. doi: 10.25046/aj0506193

- Revanna Sidamma Kavitha, Uppara Eranna, Mahendra Nanjappa Giriprasad, "A Computational Modelling and Algorithmic Design Approach of Digital Watermarking in Deep Neural Networks", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1560–1568, 2020. doi: 10.25046/aj0506187

- Bilal Babayigit, Eda Nur Hascokadar, "A Software-Defined Network Approach for The Best Hospital Localization Against Coronavirus (COVID-19)", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1537–1544, 2020. doi: 10.25046/aj0506184

- Sara Ftaimi, Tomader Mazri, "Handling Priority Data in Smart Transportation System by using Support Vector Machine Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1422–1427, 2020. doi: 10.25046/aj0506172

- Poonam Ghuli, Manoj Kartik R, Mohammed Amaan, Mridul Mohta, N Kruthik Bhushan, Poonam Ghuli, Shobha G, "Recommendation System for SmartMart-A Virtual Supermarket", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1408–1413, 2020. doi: 10.25046/aj0506170

- Ala Din Trabelsi, Hend Marouane, Faouzi Zarai, "Priority-based Scheduling Algorithm for NOMA-integrated V2X", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1225–1236, 2020. doi: 10.25046/aj0506146

- Marouane EL Midaoui, Mohammed Qbadou, Khalifa Mansouri, "A Novel Approach of Smart Logistics for the Health-Care Sector Using Genetic Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 1143–1152, 2020. doi: 10.25046/aj0506138

- Mohamed Hedi Fourati, Soumaya Marzouk, Mohamed Jmaiel, Tom Guerout, "Docker-C2A : Cost-Aware Autoscaler of Docker Containers for Microservices-based Applications", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 972–980, 2020. doi: 10.25046/aj0506116

- Hani Muhsen, Odeh Al-Amaydeh, Rakan Al-Hamlan, "Algorithm Design for Accurate Steps Counting Based on Smartphone Sensors for Indoor Applications", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 811–816, 2020. doi: 10.25046/aj050696

- Giorgia Franchini, Roberto Cavicchioli, Jia Cheng Hu, "Automatic Stochastic Dithering Techniques on GPU: Image Quality and Processing Time Improved", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 652–663, 2020. doi: 10.25046/aj050679

- Athraa Ali Kadhem, Noor Izzri Abdul Wahab, Ahmed Abdalla, "The Contribution of Wind Energy Capacity on Generation Systems Adequacy Reliability using Differential Evolution Optimization Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 331–340, 2020. doi: 10.25046/aj050640

- Moulay Youssef Smaili, Hanaa Hachimi, "Hybridization of Improved Binary Bat Algorithm for Optimizing Targeted Offers Problem in Direct Marketing Campaigns", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 239–246, 2020. doi: 10.25046/aj050628

- Pamela Zontone, Antonio Affanni, Riccardo Bernardini, Leonida Del Linz, Alessandro Piras, Roberto Rinaldo, "Supervised Learning Techniques for Stress Detection in Car Drivers", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 6, pp. 22–29, 2020. doi: 10.25046/aj050603

- Mounir Amraoui, Rachid Latif, Abdelhafid El Ouardi, Abdelouahed Tajer, "Feature Extractors Evaluation Based V-SLAM for Autonomous Vehicles", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 5, pp. 1137–1146, 2020. doi: 10.25046/aj0505138

- Chigozie Enyinna Nwankpa, "Advances in Optimisation Algorithms and Techniques for Deep Learning", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 5, pp. 563–577, 2020. doi: 10.25046/aj050570

- Kerin Augustin, Natasia, Ditdit Nugeraha Utama, "Butterfly Life Cycle Algorithm for Measuring Company’s Growth Performance Based on BSC and SWOT Perspectives", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 5, pp. 554–558, 2020. doi: 10.25046/aj050568

- Imad El Hajjami, Bachir Benhala, Hamid Bouyghf, "Shape Optimization of Planar Inductors for RF Circuits using a Metaheuristic Technique based on Evolutionary Approach", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 5, pp. 426–433, 2020. doi: 10.25046/aj050553

- Nhu-Tung Nguyen, Dung Hoang Tien, Do Duc Trung, "Multi-Objective Optimization when Surface Grinding the 3X13 Steel by Combining the General Reduced Gradient Algorithm and Harmonic Mean Method", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 5, pp. 395–400, 2020. doi: 10.25046/aj050550

- Martin Kenyeres, Jozef Kenyeres, "Applicability of Generalized Metropolis-Hastings Algorithm to Estimating Aggregate Functions in Wireless Sensor Networks", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 5, pp. 224–236, 2020. doi: 10.25046/aj050528

- Siddikov Isamiddin Xakimovich, Umurzakova Dilnoza Maxamadjonovna, "Fuzzy-logical Control Models of Nonlinear Dynamic Objects", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 4, pp. 419–423, 2020. doi: 10.25046/aj050449

- Hani AlGhanem, Mohammad Shanaa, Said Salloum, Khaled Shaalan, "The Role of KM in Enhancing AI Algorithms and Systems", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 4, pp. 388–396, 2020. doi: 10.25046/aj050445

- J. Vijay Fidelis, E. Karthikeyan, "Estimation of Influential Parameter Using Gravitational Search Optimization Algorithm for Soccer", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 3, pp. 340–348, 2020. doi: 10.25046/aj050344

- Md. Imdadul Hoque, Abul kalam Azad, Mohammad Abu Hurayra Tuhin, Zayed Us Salehin, "University Students Result Analysis and Prediction System by Decision Tree Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 3, pp. 115–122, 2020. doi: 10.25046/aj050315

- Basem Assiri, "Using Leader Election and Blockchain in E-Health", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 3, pp. 46–54, 2020. doi: 10.25046/aj050307

- Rabeb Faleh, Souhir Bedoui, Abdennaceur Kachouri, "Review on Smart Electronic Nose Coupled with Artificial Intelligence for Air Quality Monitoring", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 2, pp. 739–747, 2020. doi: 10.25046/aj050292

- Ricardo Simões Santos, António João Pina da Costa Feliciano Abreu, Joaquim José Rodrigues Monteiro, "Using Metaheuristics-Based Methods to Provide Sustainable Market Solutions, Suitable to Consumer Needs", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 2, pp. 399–410, 2020. doi: 10.25046/aj050252

- Gredion Prajena, Jeklin Harefa, Andry Chowanda, Alexander, Maskat, Kamal Rahman, Muhammad Naufal Fadhil, "The Adventure of BipBop: An Android App Pathfinding Adventure Game", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 2, pp. 299–304, 2020. doi: 10.25046/aj050239

- Ivan Aleksandrovich Tarkhanov, Galina Pavlovna Akimova, Matvey Aleksandrovich Pashkin, Aleksander Vladimirovich Soloviev, "Modelling the Methodology to Assess the Effectiveness of Distributed Information Systems", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 1, pp. 86–92, 2020. doi: 10.25046/aj050111

- Mohamed Bakry El_Mashade, Haitham Akah, Shimaa Abd El-Monem, "Windowing Accuracy Evaluation for PSLR Enhancement of SAR Image Recovery", Advances in Science, Technology and Engineering Systems Journal, vol. 5, no. 1, pp. 48–57, 2020. doi: 10.25046/aj050107

- Noor Syahirah Nordin, Mohd Arfian Ismail, Vitaliy Mezhuyev, Shahreen Kasim, Mohd Saberi Mohamad, Ashraf Osman Ibrahim, "Fuzzy Modelling using Firefly Algorithm for Phishing Detection", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 6, pp. 291–296, 2019. doi: 10.25046/aj040637

- Mohd Razif Idris, Imad Mokhtar Mosrati, "Optimization of the Electrical Discharge Machining of Powdered Metallurgical High-Speed Steel Alloy using Genetic Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 6, pp. 255–262, 2019. doi: 10.25046/aj040632

- Gustavo Gallegos Dávalos, Pedro Freddy Huamaní Navarrete, "Application of Fractal Algorithms to Identify Cardiovascular Diseases in ECG Signals", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 5, pp. 143–150, 2019. doi: 10.25046/aj040519

- Wafa Abdouni-Abdallah, Muhammad Saeed Khan, Athanasios Konstantinidis, Anne-Claude Tarot, Aziz Ouacha, "Optimization Method of Wideband Multilayer Meander-Line Polarizer using Semi-Analytical approach and Application to 6-18GHz Polarizer including test with Horn Antenna", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 5, pp. 132–138, 2019. doi: 10.25046/aj040517

- Gennadii Georgievich Cherepanov, Anatolii Ivanovich Mikhalskii, Zhanna Anatolievna Novosrltseva, "Forecasting Bio-economic Effects in the Milk Production based on the Potential of Animals for Productivity and Viability", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 5, pp. 110–114, 2019. doi: 10.25046/aj040514

- Andrei Panteleev, Valentin Panovskiy, "Application of Open-Source Optimization Library “Extremum” to the Synthesis of Feedback Control of a Satellite", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 5, pp. 23–29, 2019. doi: 10.25046/aj040503

- Houcine Marouani, Amin Sallem, Mondher Chaoui, Pedro Pereira, Nouri Masmoudi, "Multiple-Optimization based-design of RF Integrated Inductors", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 4, pp. 574–584, 2019. doi: 10.25046/aj040468

- Mohamed Hamada, Abdulsalam Latifat Ometere, Odu Nkiruka Bridget, Mohammed Hassan, Saratu Yusuf Ilu, "A Fuzzy-Based Approach and Adaptive Genetic Algorithm in Multi-Criteria Recommender Systems", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 4, pp. 449–457, 2019. doi: 10.25046/aj040454

- Alimam Mohammed Karim, Alimam Mohammed Abdellah, Seghuiouer Hamid, "Long-term Traffic Flow Forecasting Based on an Artificial Neural Network", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 4, pp. 323–327, 2019. doi: 10.25046/aj040441

- Wanwanut Boongsood, Chiranuwat Jadram, "Effects of Using Fuzzy Material Handling Inputs in the Genetic Algorithm for Machine Layout", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 4, pp. 133–140, 2019. doi: 10.25046/aj040416

- Jongsin Kim, Yonggil Choi, Younghoon Oh, "The Study of PSi & PSo Algorithm for Reducing Power of the Mobile Communication Network", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 4, pp. 47–50, 2019. doi: 10.25046/aj040406

- Yasuyuki Matsuura, Hiroki Takada, "Comparison of Electrogastrograms in Seated and Supine Positions Using Wayland Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 4, pp. 42–46, 2019. doi: 10.25046/aj040405

- Segundo Moisés Toapanta Toapanta, Adrian Alberto Chávez Monteverde, Javier Gonzalo Ortiz Rojas, Luis Enrique Mafla Gallegos, "Proposal of Ledger Technology to Apply to a Public Organization in Ecuador", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 3, pp. 251–259, 2019. doi: 10.25046/aj040333

- Amir Rizaan Rahiman, Md. Ashikul Islam, Md. Noor Derahman, "Resourceful Residual Energy Consumption in TDMA Scheduling for IoT-based Wireless Sensor Network", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 3, pp. 31–37, 2019. doi: 10.25046/aj040305

- Segundo Moisés Toapanta Toapanta, Andrés Javier Bravo Jácome, Maximo Giovanny Tandazo Espinoza, Luis Enrique Mafla Gallegos, "An Immutable Algorithm Approach to Improve the Information Security of a Process for a Public Organization of Ecuador", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 3, pp. 25–30, 2019. doi: 10.25046/aj040304

- Abba Suganda Girsang, Andi Setiadi Manalu, Ko-Wei Huang, "Feature Selection for Musical Genre Classification Using a Genetic Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 4, no. 2, pp. 162–169, 2019. doi: 10.25046/aj040221

- Abdullah Y. Al-Maliki, Kamran Iqbal, "PID-Type FLC Controller Design and Tuning for Sensorless Speed Control of DC Motor", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 6, pp. 515–522, 2018. doi: 10.25046/aj030660

- Masahiro Kanazaki, Yusuke Yamada, Masaki Nakamiya, "Multi-Objective Path Optimization of a Satellite for Multiple Active Space Debris Removal Based on a Method for the Travelling Serviceman Problem", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 6, pp. 479–488, 2018. doi: 10.25046/aj030656

- Zeinab Hajiabolhasani, Romeo Marian, John Boland, "Simulation-Optimisation of a Granularity Controlled Consumer Supply Network Using Genetic Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 6, pp. 455–468, 2018. doi: 10.25046/aj030654

- Zhijian Liu, Ni Xiao, Hui Xu, "Contract Price Model Under Active Demand Response", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 6, pp. 324–328, 2018. doi: 10.25046/aj030640

- Havva Esra Bilisik, Radosveta Sokullu, "A Novel Fair and Efficient Resource Allocation Scheduling Algorithm for Uplink in LTE-A", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 6, pp. 222–232, 2018. doi: 10.25046/aj030629

- Christos Bouras, Nikolaos Kanakis, "Evolving AL-FEC Application on 5G NGMN-Edge Computing Systems", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 5, pp. 152–160, 2018. doi: 10.25046/aj030519

- Mouhamad Chehaitly, Mohamed Tabaa, Fabrice Monteiro, Juliana Srour, Abbas Dandache, "FPGA Implementation of Ultra-High Speed and Configurable Architecture of Direct/Inverse Discrete Wavelet Packet Transform Using Shared Parallel FIR Filters", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 5, pp. 116–127, 2018. doi: 10.25046/aj030516

- Ryosuke Nakano, Yuta Takeuchi, Mikio Tsuji, Hiroyuki Deguchi, "Improvement of Transmission Characteristics in Multilayer Dual Band Filter", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 5, pp. 16–22, 2018. doi: 10.25046/aj030503

- Alaa Hamza Omran, Yaser Muhammad Abid, "Design of smart chess board that can predict the next position based on FPGA", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 4, pp. 193–200, 2018. doi: 10.25046/aj030417

- Selma Tchoketch Kebir, Mohamed Salah Ait Cheikh, Mourad Haddadi, "A detailed step-by-step electrical parameters identification method for photovoltaic generators using a combination of two approaches", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 4, pp. 45–52, 2018. doi: 10.25046/aj030406

- Ola Surakhi, Mohammad Khanafseh, Yasser Jaffal, "An enhanced Biometric-based Face Recognition System using Genetic and CRO Algorithms", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 3, pp. 116–124, 2018. doi: 10.25046/aj030316

- Mohammad Hossain, Sameer Abufardeh, Sumeet Kumar, "Frameworks for Performing on Cloud Automated Software Testing Using Swarm Intelligence Algorithm: Brief Survey", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 2, pp. 252–256, 2018. doi: 10.25046/aj030229

- Naoki Kimura, Yuya Takeda, Yoshifumi Tsuge, "Agent Based Fault Detection System for Chemical Processes using Negative Selection Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 3, no. 2, pp. 90–98, 2018. doi: 10.25046/aj030211

- Yoshiki Iwamochi, Motoki Takagi, Tasuku Miyoshi, "Flexible lengthening-shortening arm mechanism for fishery resource management", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 6, pp. 290–301, 2017. doi: 10.25046/aj020636

- Mustafa Saka, Ibrahim Eke, Suleyman Sungur Tezcan, Muslum Cengiz Taplamacioglu, "Analysis of Economic Load Dispatch with a lot of Constraints Using Vortex Search Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 6, pp. 151–156, 2017. doi: 10.25046/aj020619

- Hossein Soleymani, Amin Hasanvand, "Estimation of Power System Stabilizer Parameters Using Swarm Intelligence Techniques to Improve Small Signal Stability of Power System", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 4, pp. 139–144, 2017. doi: 10.25046/aj020419

- Md. Tanjim-Al-Akib, Lutfullahil Kabir Ashik, Krishanu Chowdhury, Md. Zahid Hasan, Hosne Al Walid, "Content Reordering Based on Mouse-tracking for Web Applications", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 3, pp. 1314–1322, 2017. doi: 10.25046/aj0203166

- Arunava Bhattacharjee, Prabal Chauhan, "Solving the SAT problem using Genetic Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 4, pp. 115–120, 2017. doi: 10.25046/aj020416

- Bui Minh Dinh, "Optimal Rotor Design of Line Start Permanent Magnet Synchronous Motor by Genetic Algorithm", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 3, pp. 1181–1187, 2017. doi: 10.25046/aj0203149

- Mouhamad Chehaitly, Mohamed Tabaa, Fabrice Monteiro, Abbas Dandache, "A Novel Ultra High Speed and Configurable Discrete Wavelet Packet Transform Architecture", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 3, pp. 1129–1136, 2017. doi: 10.25046/aj0203142

- Amin Subandi, Rini Meiyanti, Cut Lika Mestika Sandy, Rahmat Widia Sembiring, "Three-Pass Protocol Implementation in Vigenere Cipher Classic Cryptography Algorithm with Keystream Generator Modification", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 5, pp. 1–5, 2017. doi: 10.25046/aj020501

- Meriem Khelifi, Mohand Yazid Saidi, Saadi Boudjit, "Solving the Capacitated Network Design Problem in Two Steps", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 3, pp. 291–301, 2017. doi: 10.25046/aj020339

- Adrian Popovici, Mircea Băbăiţă, Petru Papazian, "Optimal Synthesis of Universal Space Vector Digital Algorithm for Matrix Converters", Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 3, pp. 147–152, 2017. doi: 10.25046/aj020319